Anterwell Technology Ltd. |

|

Dual JK flip-flop with reset; negative-edge trigger

74HC/HCT107

Dual JK flip-flop with reset; negative-edge trigger

74HC/HCT107

FEATURES

• Output capability: standard

• ICC category: flip-flops

GENERAL DESCRIPTION

The 74HC/HCT107 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A. The 74HC/HCT107 are dual negative-edge triggered JK-type flip-flops featuring individual J, K, clock (nCP) and reset (nR) inputs; also complementary Q and Q outputs. The J and K inputs must be stable one set-up time prior to the HIGH-to-LOW clock transition for predictable operation. The reset (nR) is an asynchronous active LOW input. When LOW, it overrides the clock and data inputs, forcing the Q output LOW and the Q output HIGH. Schmitt-trigger action in the clock input makes the circuit highly tolerant to slower clock rise and fall times.

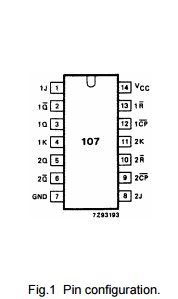

| PIN NO. | SYMBOL | NAME AND FUNCTION |

| 1, 8, 4, 11 | 1J, 2J, 1K, 2K | synchronous inputs; flip-flops 1 and 2 |

| 2, 6 | 1Q, 2Q | complement flip-flop outputs |

| 3, 5 | 1Q, 2Q | true flip-flop outputs |

| 7 | GND | ground (0 V) |

| 12, 9 | 1CP, 2CP | clock input (HIGH-to-LOW, edge-triggered) |

| 13, 10 | 1R, 2R | asynchronous reset inputs (active LOW) |

AC WAVEFORMS