Shenzhen Hongxinwei Technology Co., Ltd |

|

ATXMEGA8E5-AU 8-Bit Microcontrollers - MCU 32TQFP, IND TEMP GREEN,1.6-3.6V

1.Features

High-performance, low-power Atmel® AVR® XMEGA® 8/16-bit

Microcontroller

Nonvolatile program and data memories

8K –32KB of in-system self-programmable flash

2K – 4KB boot section

512Bytes – 1KB EEPROM

1K – 4KB internal SRAM

Peripheral features

Four-channel enhanced DMA controller with 8/16-bit address match

Eight-channel event system

Asynchronous and synchronous signal routing

Quadrature encoder with rotary filter

Three 16-bit timer/counters

One timer/counter with four output compare or input capture

channels

Two timer/counter with two output compare or input capture

channels

High resolution extension enabling down to 4ns PWM resolution

Waveform extension for control of motor, LED, lighting, H-bridge,

high drives, and more

Fault extension for safe and deterministic handling and/or

shut-down of external driver

CRC-16 (CRC-CCITT) and CRC-32 (IEEE 802.3) generator

XMEGA Custom Logic (XCL) module with timer, counter and logic

functions

Two 8-bit timer/counters with capture/compare and 16-bit cascade

mode

Connected to one USART to support custom data frame length

Connected to I/O pins and event system to do programmable logic

functions

MUX, AND, NAND, OR, NOR, XOR, XNOR, NOT, D-Flip-Flop, D Latch, RS

Latch

Two USARTs with full-duplex and single wire half-duplex

configuration

Master SPI mode

Support custom protocols with configurable data frame length up to

256-bit

System wake-up from deep sleep modes when used with internal 8MHz

oscillator

One two-wire interface with dual address match (I2C and SMBus

compatible)

Bridge configuration for simultaneous master and slave operation

Up to 1MHz bus speed support

One serial peripheral interface (SPI)

16-bit real time counter with separate oscillator and digital

correction

One sixteen-channel, 12-bit, 300ksps Analog to Digital Converter

with:

Offset and gain correction

Averaging

Over-sampling and decimation

One two-channel, 12-bit, 1Msps Digital to Analog Converter

Two Analog Comparators with window compare function and current

sources

External interrupts on all general purpose I/O pins

Programmable watchdog timer with separate on-chip ultra low power

oscillator

QTouch® library support

Capacitive touch buttons, sliders and wheels

Special microcontroller features

Power-on reset and programmable brown-out detection

Internal and external clock options with PLL

Programmable multilevel interrupt controller

Five sleep modes

Programming and debug interface

PDI (Program and Debug Interface)

I/O and Packages

26 programmable I/O pins

7x7mm 32-lead TQFP

5x5mm 32-lead VQFN

4x4mm 32-lead UQFN

Operating Voltage

1.6 – 3.6V

Operating frequency

0 – 12MHz from 1.6V

0 – 32MHz from 2.7V

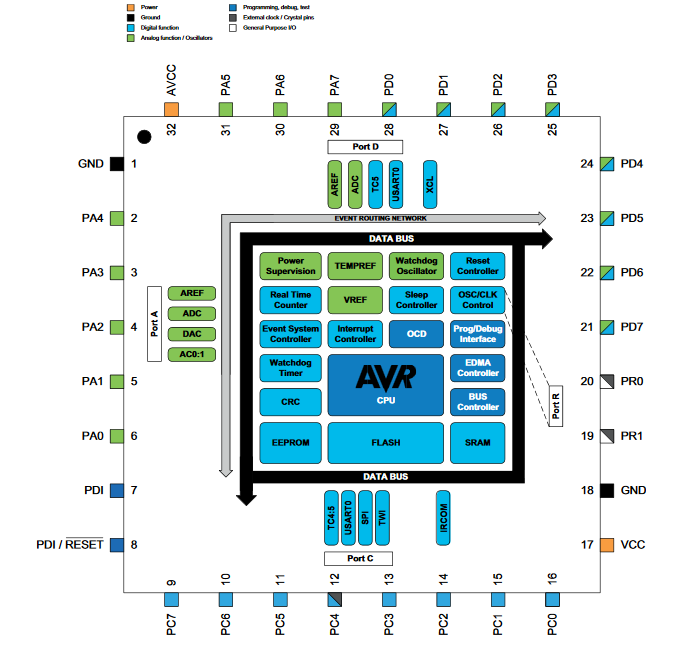

2.Pinout and Block Diagram

3.CPU

Features

8/16-bit, high-performance Atmel AVR RISC CPU

142 instructions

Hardware multiplier

32x8-bit registers directly connected to the ALU

Stack in RAM

Stack pointer accessible in I/O memory space

Direct addressing of up to 16MB of program memory and 16MB of data

memory

True 16/24-bit access to 16/24-bit I/O registers

Efficient support for 8-, 16-, and 32-bit arithmetic

Configuration change protection of system-critical features

Overview

All AVR XMEGA devices use the 8/16-bit AVR CPU. The main function

of the CPU is to execute the code and perform all calculations. The

CPU is able to access memories, perform calculations, control

peripherals, and execute the program in the flash memory. Interrupt

handling is described in a separate section, refer to “Interrupts

and Programmable Multilevel Interrupt Controller” on page 28.

Architectural Overview

In order to maximize performance and parallelism, the AVR CPU uses

a Harvard architecture with separate memories and buses for program

and data. Instructions in the program memory are executed with

single-level pipelining. While one instruction is being executed,

the next instruction is pre-fetched from the program memory. This

enables instructions to be executed on every clock cycle.

4.Why choose us?

100% new and originao with Advantage price

High efficiency

Fast Delivery

Professional team service

10 Years Experience Electronic components

Electronic components Agent

Advantage logistic discount

Excellent After-sales Service